is a comprehensive design environment with everything embedded developers need to create processing-based systems. The DE1-SoC-MTL2 delivers an integrated platform including hardware, design tools, and reference designs for developing embedded software and hardware platforms in a wide range of applications. The fully integrated kit allows developers to rapidly customize their processor and IP to best suit their specific application. The DE1-SoC-MTL2 features a DE1-SoC development board targeting Altera Cyclone® V SX SoC FPGA, as well as a capacitive LCD multimedia color touch panel which natively supports five points multi-touch and gestures.

The all-in-one embedded solution offered on the DE1-SoC-MTL2, in combination of a LCD touch panel and digital image module, provides embedded developers the ideal platform for multimedia applications with unparallel processing performance. Developers can bene

For SoC reference design in Linux for touch-screen display, please refer to the DE1-SoC-MTL2 Control Panel.

Component Solution for Altera FPGAs

| * Clock Solution | * Power Solution | * Ethernet Solution | * SDRAM Memory Solution | |||

|

|

|

|

|||

| * Inductive Component Solution | * Capacitive Component Solution | * ADC, Video, Accelerometer and Reset Generator Solution | ||||

|

|

|

Specification

DE1-SoC Development Board

Cyclone V SE SoC—5CSEMA5F31C6N

Dual-core ARM Cortex-A9 (HPS)

85K programmable logic elements

4,450 Kbits embedded memory

6 fractional PLLs

2 hard memory controllers

Configuration Sources

Serial configuration device – EPCS128 for the FPGA

On-board USB Blaster II (normal type B USB connector)

Memory Device

64MB (32Mx16) SDRAM for the FPGA

1GB (2x256MBx16) DDR3 SDRAM for the HPS

microSD card socket for the HPS

Peripherals

Two USB 2.0 Host Ports (ULPI interface with USB type A connector) on HPS

UART to USB (USB Mini B connector)

10/100/1000 Ethernet

PS/2 mouse/keyboard

IR emitter/receiver

I2C multiplexer

Connectors

Two 40-pin expansion headers

One 10-pin ADC input header

One LTC connector (one Serial Peripheral Interface (SPI) master ,one I2C bus, and one GPIO interface)

Display

24-bit VGA DAC

Audio

24-bit CODEC, Line-in, line-out, and microphone-in jacks

Video Input

TV decoder (NTSC/PAL/SECAM) and Video-in connector

ADC

sample rate: 500 KSPS

Channel number: 8

Resolution: 12 bits

Analog input range : 0 ~ 4.096 V

Switches, Buttons and LEDs

5 user keys (4 for the FPGA and 1 for the HPS)

10 user switches for the FPGA

11 user LEDs (10 for the FPGA and 1 for the HPS)

2 HPS reset buttons (HPS_RESET_n and HPS_WARM_RST_n)

Six 7-segment displays

Sensors

G-Sensor on HPS

Power

12V DC input

Capacitive Multi-touch Screen

LCD Display

7-inch TFT LCD with pixel resolution of 800*480

16 million colors (8-bit RGB)

LED backlight

Capacitive Muti-Touch

Five points multi-touch

I2C interface

Gesture supporting

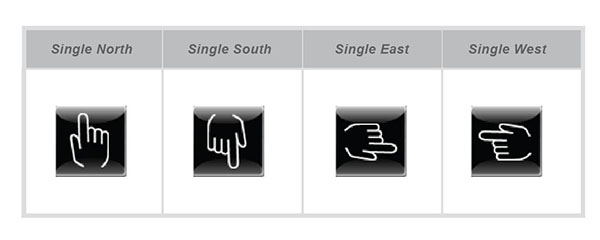

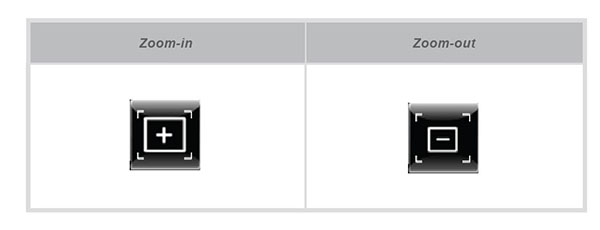

Gesture Table

One Point

Two Point

Kit Contents

Tags: SoC Platform, Intel, FPGA, DE1-SoC-MTL2, Terasic